|

1/8/2024 0 Comments Different domain iclock

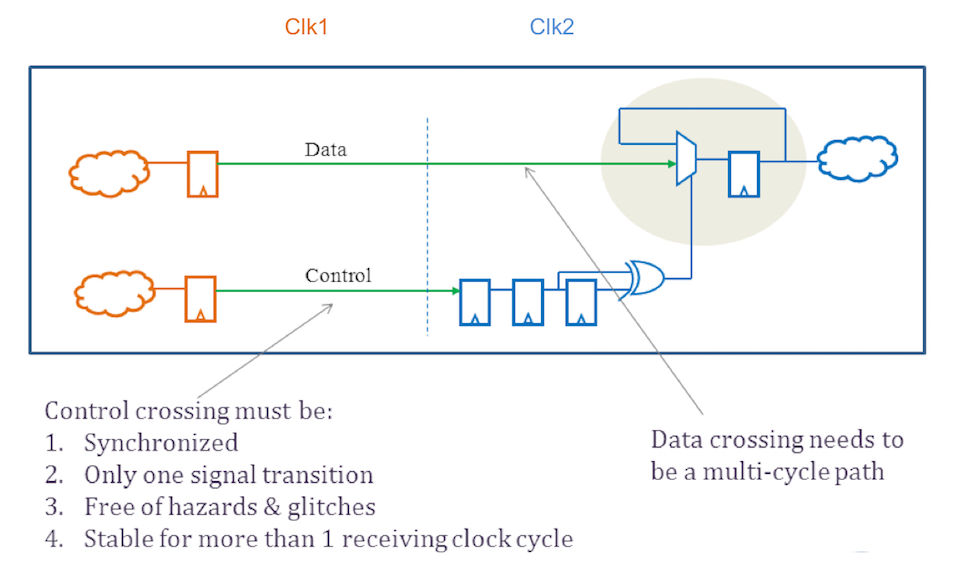

This flow requires no user input beyond specifying the input clocks and the relationships among them. Synopsys VC SpyGlass CDC is a solution that removes the limitations of older verification flows by using constraints to yield precise analysis. However, this analysis requires more powerful engines that may include formal technology. These checks resemble linting in that they analyze the design register transfer level (RTL) code or gate-level netlist to find errors. Accordingly, tools have been developed to automate checking for many CDC issues. Missing synchronizers, clock conditioning logic, and Gray encoders can be detected that way, but manual inspection is tedious and error prone. In theory, most CDC-related problems can be found by detailed code reviews. CDC errors can also occur when reset signals are not synchronized for the destination clock domain. Similarly, if two signals from the source domain are synchronized separately and then converge in the destination domain, they can be offset by one cycle. Gray Coding is often used to resolve this issue.

For a multi-bit CDC, the delay variations due to clock signal routing mean that different bits can be captured on opposite sides of a destination clock edge, corrupting the value. The probability of metastability escaping the two-stage synchronizer is very low.ĭata coherency or convergence issues can also lead to functional failures. The most common way to address this issue is adding a second flip-flop stage on the destination clock. The result can be downstream logic using an incorrect value. The destination flip-flop may enter a metastable state and its output will take some time to settle to a high or low value. The best-known CDC challenge is metastability, in which the signal from the source clock domain changes value too close to the destination clock edge. This variation can lead to signal glitches and other serious issues. As the two clocks run in parallel, their edges vary, sometimes aligning and sometimes not. A CDC occurs at every point where a signal crosses from a source clock domain to an independent, asynchronous destination clock domain. This gives the development team a lot of flexibility, but it introduces the challenges of clock domain crossing (CDC) design and verification. Many of these clocks are asynchronous to each other. On-chip buses with portions of the chip on independent clocks.Functions that can be slowed down to conserve power.Licensed IP blocks within the chip requiring different clock speeds.Multiple external interfaces with distinct clock requirements.

There are several reasons for this explosion: Several dozen different clocks are common in today’s chips, with some designs having more than a thousand domains. The number of clock domains is also increasing steadily. As chips grow ever larger and more complex, gate count and amount of embedded memory grow dramatically.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed